你是否曾想過,為何智能手機能夠流暢運行多任務?為何自動駕駛汽車能精準協調傳感器與控制系統?答案或許就藏在那些微小卻至關重要的組件中——時鐘發生器。作為電子設備的“節拍器”,它通過生成穩定的時序信號,確保系統各部分協同工作。在高速運算、物聯網和人工智能蓬勃發展的今天,時鐘發生器的技術優勢正成為設備性能突破的關鍵推手。

一、精確時序控制:電子系統的“指揮家”

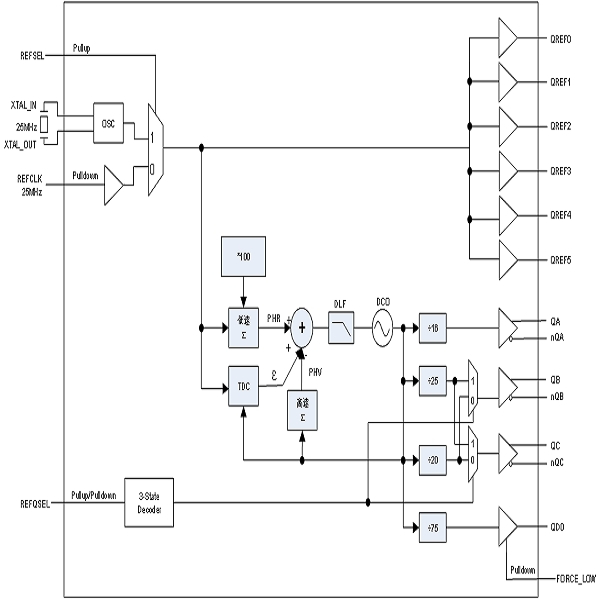

時鐘發生器的核心功能是產生高精度時鐘信號,這類信號如同交響樂團的指揮棒,為處理器、存儲器、傳感器等組件提供統一的時序基準。以CPU為例,其每秒數十億次運算需要嚴格的時鐘同步,否則可能導致數據讀寫沖突或邏輯錯誤。

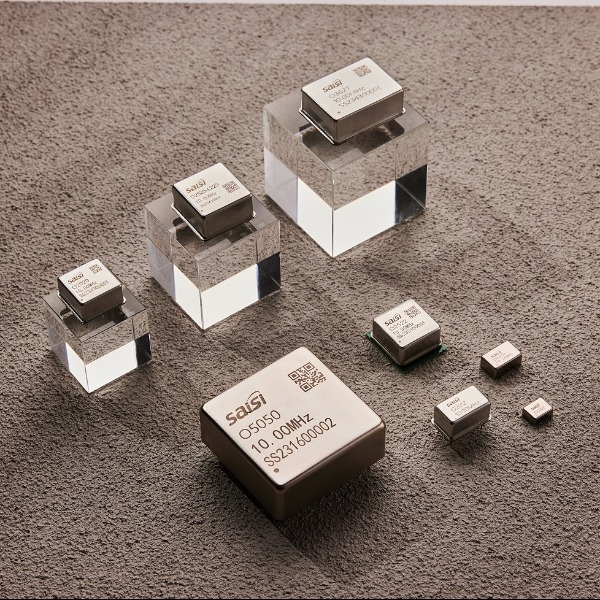

通過采用溫度補償晶體振蕩器(TCXO)或壓控晶體振蕩器(VCXO),現代時鐘發生器可將頻率誤差控制在±0.1ppm(百萬分之一)以內。例如,在5G基站中,這種精度確保了不同頻段信號的無縫切換,將網絡延遲降低至毫秒級。

二、提升系統穩定性:從抗干擾到低抖動

電子設備的工作環境往往充滿電磁干擾(EMI)和電壓波動,而時鐘發生器的低抖動(Jitter)特性能顯著提升信號完整性。抖動值越低,信號邊沿越清晰,數據傳輸的誤碼率(BER)也隨之下降。

實驗數據顯示,采用鎖相環(PLL)技術的時鐘發生器,可將相位噪聲降低至-150dBc/Hz@1MHz偏移,這對高速SerDes(串行器/解串器)接口尤為重要。例如,HDMI 2.1標準要求時鐘抖動小于200fs(飛秒),只有高性能時鐘發生器能滿足這一嚴苛條件。

三、靈活性與可編程性:應對多樣化需求

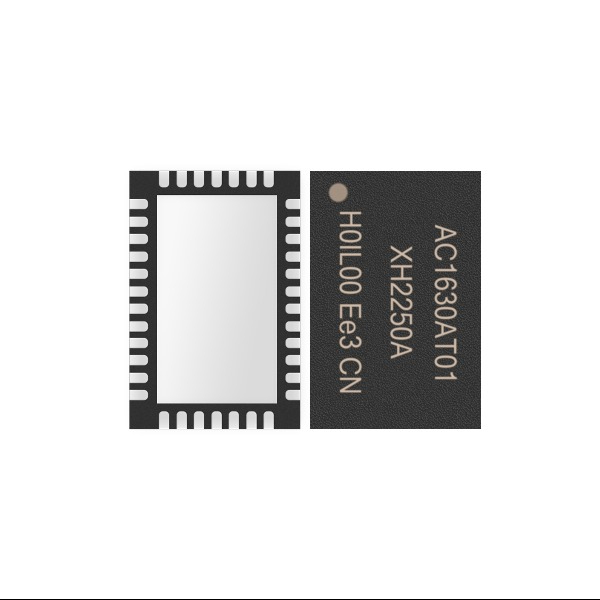

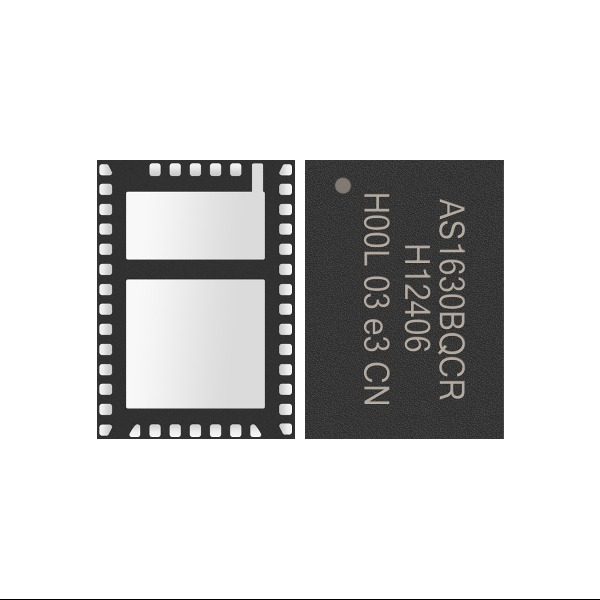

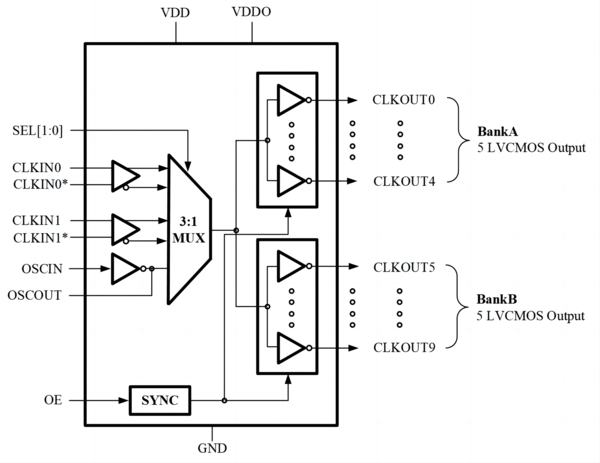

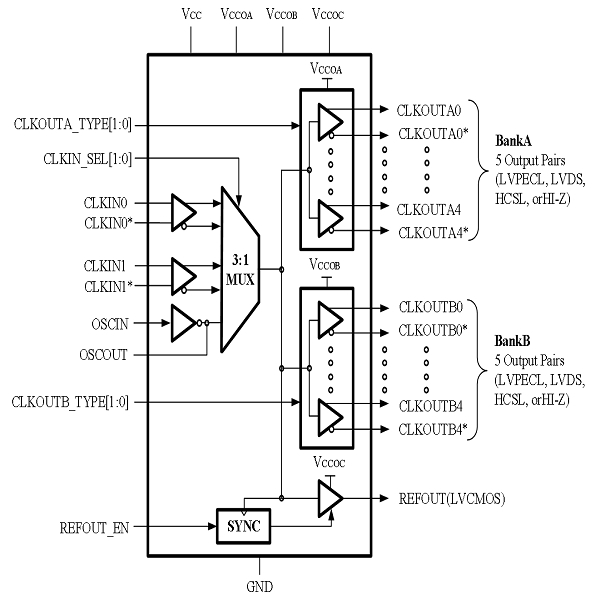

傳統固定頻率時鐘源已無法適應現代設備的動態需求,而可編程時鐘發生器通過軟件配置,可實時調整輸出頻率、占空比和電平標準。這種靈活性在FPGA、AI芯片等場景中尤為關鍵。

以數據中心為例,服務器在不同負載下需要動態切換CPU頻率以平衡性能與功耗。支持I2C或SPI接口的時鐘發生器,可在微秒級內完成頻率切換,幫助能效比提升30%以上。此外,多路輸出功能還能減少PCB板上的時鐘樹復雜度,節省布局空間。

四、低功耗設計:綠色科技的隱形推手

隨著物聯網設備向小型化與電池供電方向演進,時鐘發生器的功耗表現直接影響終端產品的續航能力。低功耗時鐘芯片通過優化電路架構(如使用CMOS工藝)和智能啟停技術,將工作電流降至微安級。

五、多領域融合應用:從消費電子到工業4.0

時鐘發生器的優勢不僅限于消費電子領域。在工業自動化中,高精度時鐘同步是EtherCAT、Profinet等實時以太網協議的基礎;在汽車電子中,車載攝像頭與雷達依賴納秒級同步信號實現障礙物精準測距;而在航空航天領域,抗輻射加固設計的時鐘發生器能承受極端溫度與宇宙射線干擾。

通過以上分析可見,時鐘發生器不僅是電子設備的“心跳”,更是技術創新與產業升級的基石。從納米級制程芯片到TB級數據中心,從穿戴設備到智慧城市,其核心優勢——精確、穩定、靈活、高效——將持續驅動未來科技的邊界拓展。

時鐘系統

時鐘系統

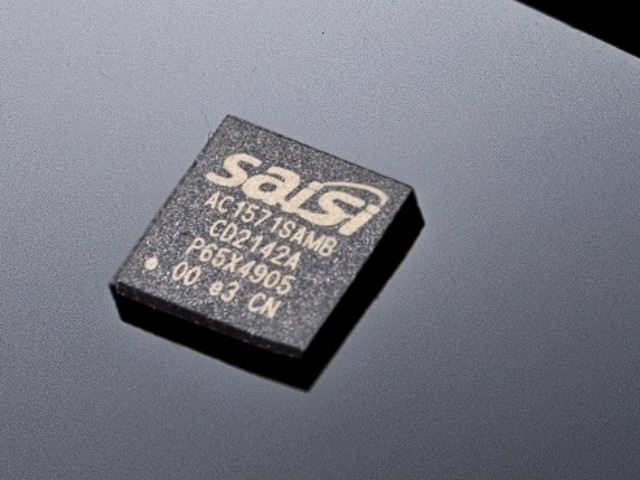

芯片

芯片

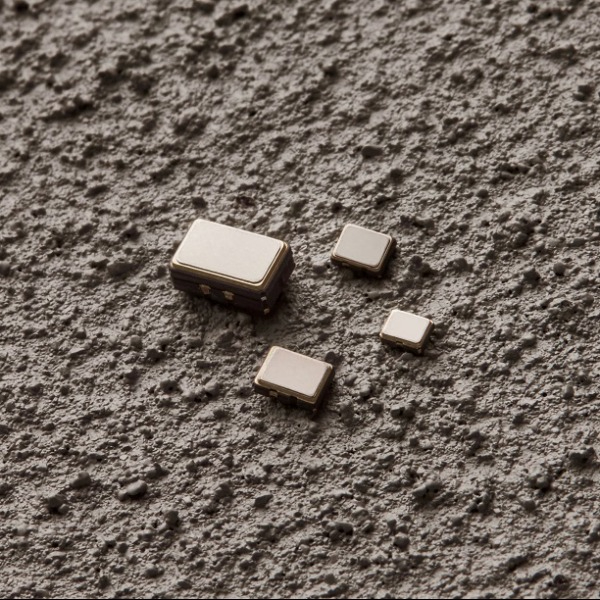

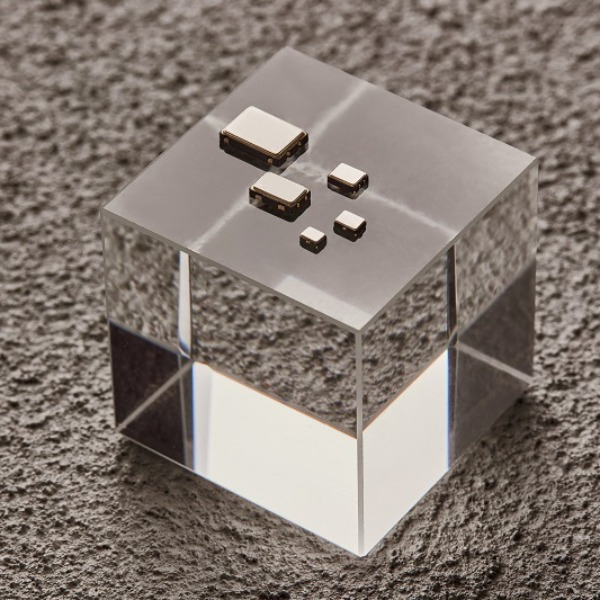

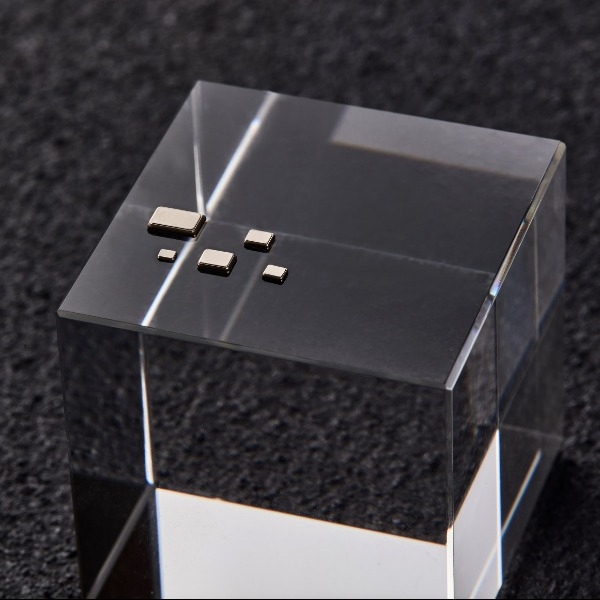

晶振&原子鐘

晶振&原子鐘

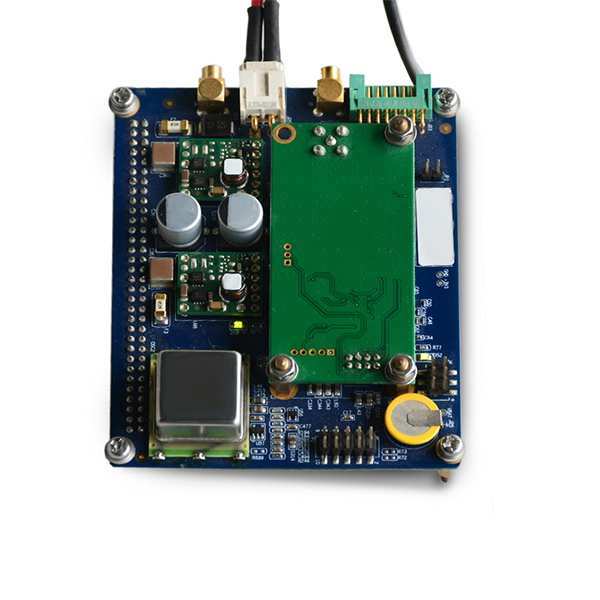

授時板卡

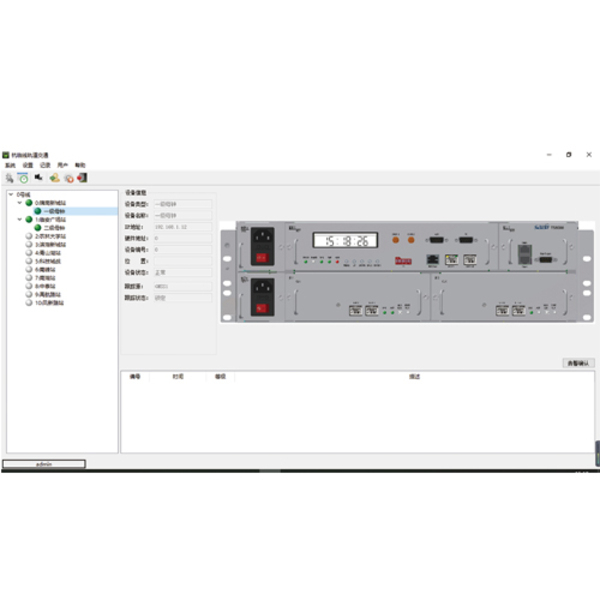

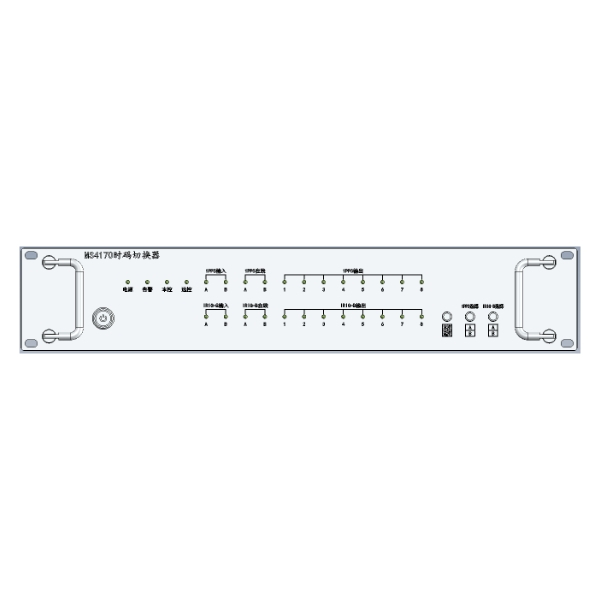

NTP時間同步服務器PTP時間同步服務器時間同步裝置授時安全防護裝置網同步設備/時頻一體化設備子母鐘系統BBU池時間同步時統設備鐘組設備測試儀器光纖雙向設備網管系統語音芯片時鐘發生器時鐘緩沖器時鐘SOC芯片晶振原子鐘授時模塊

授時板卡

NTP時間同步服務器PTP時間同步服務器時間同步裝置授時安全防護裝置網同步設備/時頻一體化設備子母鐘系統BBU池時間同步時統設備鐘組設備測試儀器光纖雙向設備網管系統語音芯片時鐘發生器時鐘緩沖器時鐘SOC芯片晶振原子鐘授時模塊

智能電網

智能電網

通信網絡

通信網絡

智慧交通

智慧交通

智能樓宇

智能樓宇

數據中心

數據中心

前沿領域

前沿領域

新聞資訊

新聞資訊

人才研學中心

人才研學中心

加入賽思

加入賽思

關于賽思

關于賽思